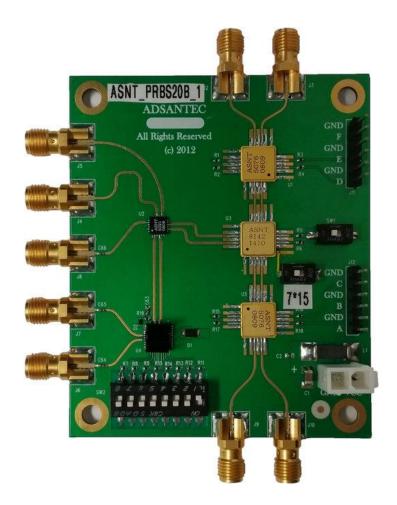

#### ASNT\_PRBS20B\_1

# 18Gbps PRBS7/15 Generator Featuring Jitter Insertion, Selectable Sync, and Output Amplitude Control

- Broadband frequency range from 20*Mbps* 18.0*Gbps*

- Minimal insertion jitter

- Fast rise and fall times

- Two PRBS data output, jitter insertion capability, and output amplitude control from 0V to 1V peak to peak.

- Up to 155ps delay variation on each output

- Differential clock output

- 50% duty cycle for sync output on all divide ratios

- Sync output and Clock input are AC coupled on board

- Single positive 3.3V supply

#### DESCRIPTION

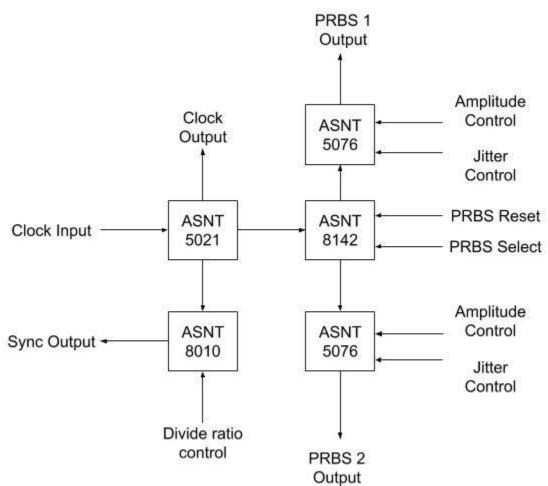

#### Fig. 1. Functional Block Diagram

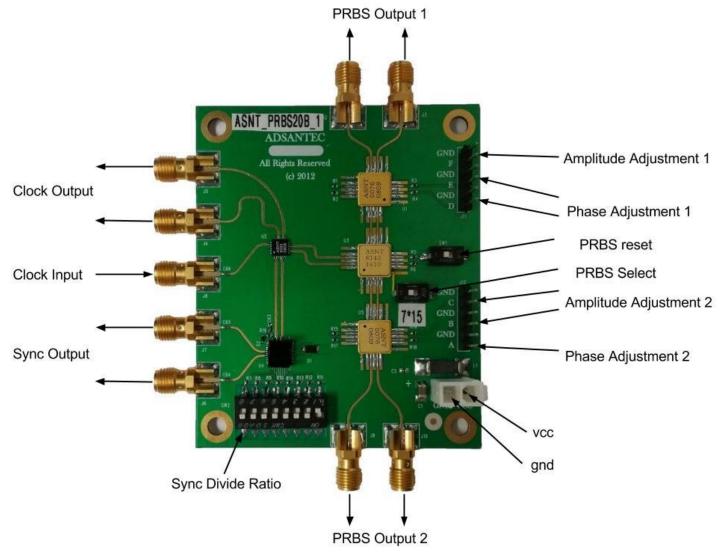

The ASNT PRBS20B 1 is a broadband 2<sup>7</sup>-1 or 2<sup>15</sup>-1 PRBS generator intended for test, prototyping, microwave, and communication applications. The amplitude and phase are adjustable on both differential outputs. There is jitter/phase shift insertion onto either differential output with a bandwidth up to 500 kHz. Output amplitude on both PRBS outputs varies from 0V to 1V single-ended peak to peak. A single-ended clock from 10MHz to 18GHz with an amplitude as low as 50mV peak to peak may be applied to the clock input. A buffered differential clock output is provided. A differential Sync Output divides an input clock from 1 to 256. When using an oscilloscope, the Sync Output triggers the oscilloscope. The system is capable of triggering for an eye diagram for PRBS7/PRBS15 or PRBS7 pattern with divide ratios 127 or 254, and it uses an on-board PRBS reset switch to preset the generator avoiding the all zero state lock-up. An on-board Pattern Select switch selects either PRBS7 or PRBS15.

The ASNT\_PRBS20B\_1 board contains nine Emerson SMA connectors MFG PN: 142-0761-881, 500hm transmission lines to the device, and power supply decoupling networks on the evaluation board. Power is supplied through a two-pin MOLEX connector P/N: 39-28-1023.

Eye diagram

pattern pattern

#### SYNC OUTPUT

The Sync Output can be configured to output any divide ratio from 1 to 256 from the clock input. It contains eight switches that represent 8 bits. The LSB starts at SW1 and the MSB ends at SW8. The binary value of zero gives a decimal n value of 256. Increasing binary values increases the decimal value n.

| - VCVLL · VCVLL ·            |                          |                 |

|------------------------------|--------------------------|-----------------|

|                              | DIP SW #                 | n Divide Ratio  |

| DC/ D5, D4 91 97 99 99 910 5 | 87654321                 | II Divide Ratio |

| R6 R5 R4 R3 R7 R8 R9 R10     | $0\ 0\ 0\ 0\ 0\ 0\ 1$    | 1               |

|                              | 00000010                 | 2               |

|                              | $0\ 0\ 0\ 0\ 0\ 0\ 1\ 1$ | 3               |

| "0"                          | 00010000                 | 16              |

| J7 2 2 2 2 2 2 2 2 2 3 1 1 1 | •                        |                 |

|                              | •                        |                 |

|                              | 01111111                 | 127             |

| 1 3 3 3 3 3 3 3 3 3 1        | 11111110                 | 254             |

|                              | 00000000                 | 256             |

## ABSOLUTE MAXIMUM RATINGS

Caution: Exceeding the absolute maximum ratings shown in Table 1 may cause damage to this product and/or lead to reduced reliability. Functional performance specified over the recommended operating conditions for power supply and temperature only. AC and DC device characteristics at or beyond the absolute maximum ratings are not assumed nor implied. All min and max voltage limits are in reference to ground.

| Parameter                   | Min | Max  | Units |

|-----------------------------|-----|------|-------|

| Supply Voltage (VCC)        |     | +3.6 | V     |

| Power Consumption           |     | 8    | W     |

| RF Input Voltage Swing (SE) |     | 1.0  | V     |

| Case Temperature            |     | +90  | °С    |

| Storage Temperature         | -40 | +100 | °С    |

| Operational Humidity        | 10  | 98   | %     |

| Storage Humidity            | 10  | 98   | %     |

| Table  | 1. | Absolute   | Maximum        | Ratings  |

|--------|----|------------|----------------|----------|

| 1 0000 |    | 1105011110 | 11100/00/00/00 | 10000050 |

## **TERMINAL FUNCTIONS**

### **OPERATION**

1. Measure 50*Ohms* on all nine SMA connectors referenced to vcc.

(NOTE: On board AC coupling prevents direct measurements on all connectors. These values must be measured at the trace referenced to **vcc**.)

2. Measure 390*Ohms* on headers D and E referenced to vcc. Measure 2.2*kOhms* on headers B and C referenced to vcc. Measure 150*Ohms* on header A and 2*kOhms* on header F referenced to vcc.

(A deviance of up to 10% in these values is within specification.)

- 3. Connect the board to a power supply set to 0V with a current limit of 2.2A.

- 4. Slowly increase the power supply to + 3.3V. Nominal current is 2.1A.

- 5. Apply a DC coupled clock to the Clock Input up to  $18GH_z$  with peak-to-peak amplitude from 50mV to 1V. Note: Clock input is AC coupled on-board.

- 6. Connect the PRBS outputs AC coupled to a 50*Ohms* terminated oscilloscope. Place 50*Ohms* AC coupled terminations on all unused input/outputs.

- 7. Set PRBS Select to the ON position to select PRBS15 or OFF to select PRBS7.

- 8. Turn PRBS reset to the ON position and then back to the OFF position to reset the PRBS generator.

- 10. To add jitter or change phase on the PRBS 1 output, apply a 2.1*V* to 3.3*V* to header pin E and float (do not connect) pin D to decrease phase shift. Apply 2.1*V* to 3.3*V* to header pin D and float (do not connect) header pin E to increase phase shift.

- 11. To change the amplitude on the PRBS 1 output, apply a positive voltage ranging from 2.5V to 3.3V to header pin F. The amplitude control for the PRBS 1 output is single-ended only.

- 12. To change the amplitude on the PRBS 2 output, apply a voltage ranging from 2.5V to 3.3V to header pin B and float (do not connect) pin C to increase amplitude. Apply a voltage ranging from 2.5V to 3.3V to header pin C and float (do not connect) header pin B to decrease amplitude.

- 13. To add jitter or change phase on the PRBS 2 output, apply a positive voltage ranging from 2.1V to 3.3V to header pin A. The delay control for the PRBS 2 output is single-ended only.

ADSANTEG

Ultra High-Speed Mixed Signal ASICs

Offices: 310-530-9400 / Fax: 310-530-9402 www.adsantec.com

# **ELECTRICAL CHARACTERISTICS**

| PARAMETER                  | MIN       | ТҮР      | MAX         | UNIT             | COMMENTS         |

|----------------------------|-----------|----------|-------------|------------------|------------------|

| vee                        |           | 0        |             | V                | External ground  |

| VCC                        | 3.1       | 3.3      | 3.5         | V                |                  |

| I <sub>VCC</sub>           | 1.7       | 2.1      | 2.5         | A                |                  |

| Power                      |           | 6.9      |             | W                |                  |

| Operating Temperature      | -25       | 50       | 85          | °C               |                  |

|                            |           | Clock I  | nput        |                  |                  |

| Frequency                  | 0.02      |          | 18          | GHz              |                  |

| Single-Ended Swing         | 50        | 400      | 1000        | mV <sub>PP</sub> |                  |

|                            |           | Clock C  | output      |                  |                  |

| Frequency                  | 0.02      |          | 18          | GHz              |                  |

| Single-Ended Swing         | 570       | 600      | 630         | mV <sub>PP</sub> |                  |

| Common Mode Level          | vcc -0.35 | vcc -0.3 | 3 vcc -0.25 |                  |                  |

| Additive Jitter            |           |          | 5           | ps               | Peak-to-Peak     |

| Duty Cycle                 | 45        | 5 50     | 55          | %                | For Clock Signal |

|                            |           | Sync O   | utput       |                  |                  |

| Frequency                  | 0.01      |          | 18          | GHz              |                  |

| Single-Ended Swing         | 570       | 600      | 630         | mV <sub>PP</sub> |                  |

| Rise/Fall Times            | 15        | 17       | 19          | ps               | 20%-80%          |

| Duty Cycle                 | 45%       | 50%      | 55%         |                  | For clock signal |

|                            | I         | PRBS_1   | Output      |                  |                  |

| Single-Ended Voltage Level | 475       | 500      | 525         | mV <sub>PP</sub> |                  |

| Common Mode Level          | vcc -0.3  | vcc -0.2 | 25 vcc -0.2 | V                | When Tn is NC    |

| Duty Cycle                 | 45        | 50       | 55          | %                |                  |

## **ELECTRICAL CHARACTERISTICS (CONTINUED)**

| PARAMETER                  | MIN      | ТҮР         | MAX      | UNIT      | COMMENTS      |  |

|----------------------------|----------|-------------|----------|-----------|---------------|--|

| PRBS_2 Output              |          |             |          |           |               |  |

| Single-Ended Voltage Level | 475      | 500         | 525      | $mV_{PP}$ |               |  |

| Common Mode Level          | vcc -0.3 | vcc -0.25   | vcc -0.2 | V         | When Tn is NC |  |

| Duty Cycle                 | 45%      | 50%         | 55%      |           |               |  |

|                            | Amp      | olitude Con | trol     |           |               |  |

| Differential Swing         | -2.85    |             | 2.85     | $mV_{PP}$ |               |  |

| Common Mode Level          | vcc -0.5 | vcc -0.25   | VCC      | V         |               |  |

| Amplitude Variation        | 0        | 500         | 1000     | V         |               |  |

| Bandwidth                  | 0.0      |             | 100      | kHz.      |               |  |

| Jitter Control             |          |             |          |           |               |  |

| Differential Swing         | -3.8     |             | 3.8      | $mV_{PP}$ |               |  |

| Common Mode Level          | vcc -0.5 | vcc -0.25   | VCC      | V         |               |  |

| Phase Shift Control        | 0        |             | 155      | ps        |               |  |

| Shift Stability            | -12      |             | 12       | ps        | 0-125°C       |  |

| Bandwidth                  | 0.0      |             | 500      | kHz       |               |  |

## **REVISION HISTORY**

| Revision | Date    | Changes                                                          |  |  |

|----------|---------|------------------------------------------------------------------|--|--|

| 1.5.2    | 08-2020 | Updated Ohmic Values, Sensitivity and Electrical Characteristics |  |  |

| 1.4.2    | 02-2020 | Corrected Header Control Voltage Values                          |  |  |

| 1.3.2    | 07-2019 | Updated Letterhead                                               |  |  |

| 1.3.1    | 04-2019 | Added P/N and connector description to board description         |  |  |

| 1.2.1    | 08-2015 | Correction Operation #2. Current limit increased to 2.2A from 2A |  |  |

| 1.1.1    | 04-2015 | Changed page 1 picture and terminal function picture             |  |  |

|          |         | Changed Ivcc current and power                                   |  |  |

|          |         | Corrected Operation #6                                           |  |  |

| 1.0.1    | 04-2015 | Initial Release                                                  |  |  |